[Total No. of Questions -9] (2127) [Total No. of Printed

5503

B.Tech. 3rd Semester Examination

Data Structure and Algorithms (CSE) Chart.

Paper - IT (ID) 3003

Time Allowed: 3 Hours

Maximum Marks: 100

The candidates shall limit their answers precisely with the nswer-book (40 pages) issued to them and no supplementary/continuation sheet will be issued.

Note: Candidates are required to attempt five questions in all selecting at least one question from each section A, B, C and Section D. Entire Section E is compulsory.

## SECTION - A

- Discuss in brief the uses of data structures. Differentiate between linear and non-linear data structures. Discuss in brief the concept of algorithmic complexity and time space trade off.

- 2. Define a linked list. How a linear linked list is different from doubly linked list. Write an algorithm to insert and delete a node in a doubly linked list. (15)

## **SECTION - B**

(a) Discuss various tree traversals in detail giving suitable examples. (08) (b) Write an algorithm to insert an element in a binary search tree (07)

5503

4. What is binary search tree? How it is different from binary tree? Write an algorithm to delete a node from a binary search tree. (15)

(2)

## **SECTION - C**

What do you mean by a graph? Discuss various methods of representing the graph in memory giving merits and demerits of each method. (15)

Write short note on the following

(a) Simple graph (04)

(04) Multi graph

(c) Acyclic Graph (04)

(d) Connected graph (03)

## SECTION - D

Explain the procedure of merge sort giving suitable example. (15)

[P.T.O.]

5503

Explain the linear search in detail. List down the conditions where linear search is preferred over binary search. (15)

#### SECTION - E

- 9. (a) Give the advantages of linked list. (04)

- (b) How a linked list is represented in memory? (04)

- (c) Define the weigh of a tree and give an example.(04)

- (d) Differentiate between graph and a tree. (04)

- (e) What do you mean by hashing? Discuss in brief.(04)

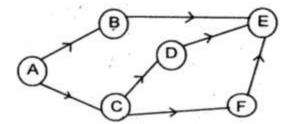

- (f) Give the BFS and DFS of the following graph.

(04)

[P.T.O.]

(g) Discuss various applications of graph in brief. (04)

(4)

- (h) Compare selection sort with bubble sort. (04)

- (i) Which data structure is best suited for the insertion sort and why? (04)

- (j) How a tree is represented in memory? (04)

884

Total No. of Questions - 9] (2118)

Total Pages: 3

# 5922

## B.Tech. IIIrd Semester Examination DATA STRUCTURE AND ALGORITHM (CSE/IT)

Paper: IT(ID) - 3003

Time: Three Hours]

[Maximum Marks: 100

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary/continuation sheet will be issued.

Note: Attempt five questions in all, selecting one each from Sections A, B, C and D. Section E is compulsory.

## SECTION-A

- What are the various measures of complexity of an algorithm? Discuss each of them with example.

- What is a Doubly link list? Write algorithm for each of the operation possible on Doubly link list.

#### SECTION-B

- 3. Giving a Binary tree T, write algorithm to

- (a) count the number of Non-leaf elements of T.

- (b) check if the tree is balanced.

15

5922/1200/GGG/106

[P.T.O.

4. What is a Binary search tree? Write the operation of insertion and deletion in a Binary search tree.

15

#### SECTION-C

- 5. What are the various techniques for representation of graph?

Explain each of them with example.

15

- Explain the Dijkstra's algorithm to find the shortest distance in a weighted graph.

#### SECTION-D

- Explain the following searching algorithm with their complexity:

- (a) Binary search.

- (b) Linear search.

15

8. Give an array:

17 8 2 3 6 12 14 1 15

How these will be sorted in the following:

- (a) Radix sort.

- (b) Selection sort.

- (c) Bubble sort.

15

#### SECTION-E

- 9. Attempt all the following:

- (a) What is the complexity of Insertion sort?

- (b) What is a Data structure?

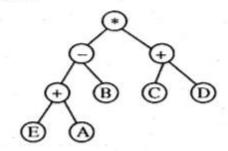

- (c) Convert a ^ b ^ c + d \* e f into postfix expression.

- (d) Define Heap.

5922/1200/GGG/106

2

- (e) What is a Circular link list?

- (f) What is a B-tree ?

- (g) What is a Height balanced tree ?

- (h) What is an AYL tree ?

- (i) How a node is represented in C?

- (j) How an element is searched in singly link list?

$4 \times 10 = 40$

Total No. of Questions -- 9

Total Pages: 3

(2119)

## B.Tech. IIIrd Semester Examination

## DATA STRUCTURE AND ALGORITHM (CSE/IT)

Paper: IT(ID) - 3003

Time: Three Hours]

[Maximum Marks: 100

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary/ continuation sheet will be issued.

Note: Attempt five questions in all, selecting at least one question each from Section A, B, C & D. Section E is compulsory.

#### SECTION-A

- What is Complexity of an algorithm? How is it measured? Discuss Time space trade off with an example.

- Write an algorithm to insert an element in two-way link list.

#### SECTION-B

- (a) Build a heap tree from following list of numbers : 44, 30, 50, 22, 60, 55, 77 and 55. 15

- (b) What is AVL tree ?

5132/1400/GGG/103

[P.T.O.

- (a) Write an algorithm for INORDER traversal of a binary tree.

- Traverse the given tree in Preorder, Inorder and Post-order

#### SECTION-C

Write Dijkstra's algorithm for shortest path.

20

What do you mean by Adjacency mátrix ? Give an example and explain how it is used in graphs. 20

#### SECTION-D

- Write an algorithm for insertion sort and explain it with 7. an example. 20

- Assume we have a sorted array of elements in descending order. Can binary search algorithm still be implemented on it? If yes, write the modified algorithm. If not justify.

5132/1400/GGG/103

## SECTION-E

- Write short answers of the following:

- (a) Give applications of Linked list.

- (b) What is height of a tree?

- (c) What is Complete binary tree ?

- (d) Differentiate between Graph and Tree.

- (e) Give complexity of Selection sort and Bubble sort.

- (f) What is Hash table ?

- (g) What is Collision?

- (h) Convert A\*(B + D)/E F\*(G + H/K) into Post-fix expression.

- Differentiate between Binary search and Linear search.

- (j) What is Big O notation ?

$2 \times 10 = 20$

(2115)

5885

Total Pages: 3

B. Tech. 3rd Semester Examination

DIGITAL ELECTRONICS

Paper-EC-ID 3001

(EE/ECE/CSE/IT)

(New Syllabus)

Time: Three Hours

Maximum Marks: 100

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary/continuation sheet will be issued.

Note: Attempt one question each from Sections-A, B, C and D and entire Section-E.

#### Section-A

1 Fill in the blanks (?)

| Binary   | Octal | BCD  | Hexadecima |

|----------|-------|------|------------|

| 11110101 | 365?  | ?    | ?          |

| . ? -    | 4567  | ?    | ?          |

| ?        | ?     | 3456 | ?          |

| ?        | ?     | ?    | 9-abc      |

20

- (a) What is error detection and correction code Hamming code? Explain with the help of an example.

- Perform following subtraction using 2's Complement method:

- (i) 11111100-01010100

- (ii) 11110001-10001111.

6

5885/1,600 (Q-9) [P.T.O.]

5885

- (c) Perform following subtraction using 10's Complement method:

- (i) 97-45

- (ii) 44-87

#### Section-B

Minimize the following Boolean expression using quine Mccluskey procedure

$f(v, w, x, y, z) = \Sigma(0, 14, 5, 7, 8, 9, 13, 15, 17, 19, 21) + \Sigma dc(12, 14, 23).$ Verify the result using K map.

Write down the truth table of a full adder circuit and realize it using (i) 9 Nand gate (ii) 8:1 Multiplexer (iii) 4:1 Multiplexer.

#### Section-C

- 5. Draw the diagram of DCTLd gate and explain its operation.

Why Base current hogging is there?

20

- 6. Draw the Diagram of an Ex = or gate using MOS gates. 20

## Section-D

- Write down the truth table of all flip-flops. Draw the diagram of j-k flip-flop and explain its operation.

- (a) Draw the diagram of any A-D Convertor and explain its operation.

- (b) Draw the diagram of shift register and explain its operation as SISO, PISO, PIPO, SIPO. 10

5885

(2)

# 5885

#### Section-E

| ). | (a)                                                  | What is a positive logic and negative logic?               | 2   |  |  |  |

|----|------------------------------------------------------|------------------------------------------------------------|-----|--|--|--|

| A  | (b)                                                  | Draw the truth table of all logic gates.                   | 2   |  |  |  |

|    | (c)                                                  | Realize an AND gate using NOR gates only.                  | 2   |  |  |  |

|    | (d)                                                  | What is the difference between multiplexer a               | ind |  |  |  |

|    |                                                      | demultiplexer ?                                            | 2   |  |  |  |

|    | (e)                                                  | Give comparison between various A-D converters ?           | 2   |  |  |  |

|    | (f)                                                  | What is the difference between ROM and RAM ? 2             |     |  |  |  |

|    | (g) How Race around condition is eliminated in Maste |                                                            |     |  |  |  |

|    |                                                      | slave J-k flip-flop ?                                      | 2   |  |  |  |

|    | (h)                                                  | Perform following binary subtraction:                      |     |  |  |  |

|    |                                                      | 0101010-11010101                                           | 2   |  |  |  |

|    | (خل                                                  | Convert following binary number into gray code vice-versa: | and |  |  |  |

|    |                                                      | 10101111                                                   | 2   |  |  |  |

|    | (j)                                                  | Define Multiplexer and Demultiplexer.                      | 2   |  |  |  |

of Printed Pages: 3

(2116)

B.Tech. 3rd Semester Examination DIGITAL ELECTRONICS (FE/ECE/CSE/IT)

Paper - EC (ID) 3001

Time Allowed: 3 Hours

Maximum Marks: 100

note:- The candidates shall limit their answers precisely with the answer-book (40 pages) issued to them and no supplementary/continuation sheet will be issued.

Attempt one question from each section and entire section E.

## SECTION - A

Fill in the blanks shown with?

| Binary    | Octal   | Decimal | Hexadecimal |  |

|-----------|---------|---------|-------------|--|

| 1011 1101 | ?       | ?       | ?           |  |

| ?         | 7654321 | . ?     | ?           |  |

| ? ?       | ?       | 123456  | ?           |  |

| ?         | ? .     | ?       | 1234        |  |

- What are various error-correcting codes? Discuss them briefly.

- Perform BCD addition (I) 65 + 78

- Perform BCD Subtraction 78-76

15

[P.T.O]

5066/1800

5066

## SECTION - B

- What do you understand by K-Map? Minimize the following Boolean expression using K-Map :  $F_1(w, x, y, z) = \Sigma(0, 1, 4, 5, 7, 8, 9, 13, 15) + \Sigma dc(12, 14).$ Verify your result using Quine Mccluskey procedure.

- Write down the truth table of full subtarctor and realize it through N and gates only.

## SECTION - C

- What is CMOS gate? Explain its operation. Draw an x-or gate using MOS gates.

- Draw the diagram of an ECL gate and explain its operation.

## SECTION - D

- Draw a diagram Write down truth table of various flipflops. What is a Race around condition? How ir eliminated in Master Slave J-K Flip-flop? Draw its diagram.

- Draw the diagram 555 timer and explain its operation in an astable mode.

- Draw the diagram of an A-D convertor and explain its operation.

# SECTION - E

| 9. | (a         | Convert the following numbers to hexadecimal number and vice versa : (i) 11111010 (ii) 11101000 |

|----|------------|-------------------------------------------------------------------------------------------------|

|    | 3 - 5      | 4                                                                                               |

|    | (b)        | Why 2's complement is used in computers for representation of negative numbers?                 |

| Ä  | (c)        | Realize an And gate using NOR gates only. 4                                                     |

|    | (d)        | Differentiate between combinational circuit and sequential circuit?                             |

|    | (e)        | State various postulates and theorems of Boolean algebra                                        |

|    | <b>(f)</b> | Differentiate between minterm and maxterm. 4                                                    |

| 1  | (g)        | Perform following binary subtraction : 11111111-11010101                                        |

|    | (h)        | What do you mean by an error?                                                                   |

|    | (i)        | List the steps in designing a synchronous counter4                                              |

|    | 0          | Write down truth table for EX-OR gate. 4                                                        |

|    |            |                                                                                                 |

[Total No. of Questions -9]

[Total No. of Printed Pages :4]

(2127)

## 5495-A

# B.Tech. 3rd Semester Examination Digital Electronics (EE/ECE/CSE/IT)

Paper - EC(ID) - 3001

Time Allowed: 3 Hours

Maximum Marks: 100.

The candidates shall limit their answers precisely with the answer-book (40 pages) issued to them and no supplementary/continuation sheet will be issued.

Note: Attempt One question from section A, B, C, D & entire E section.

## **SECTION - A**

- I. (A) Convert decimal number (39.12) in binary form?

- (B) Multiply (10.1)<sub>2</sub> & (1.01)<sub>2</sub> & convert the result into equivalent decimal number.

- (C) Divide (1EC 87)<sub>16</sub> by (A5)<sub>16</sub>. (15)

- II. Write short note on.

- (A) Floating point representation & its significance?

- (B) Error detection code & its features?

- (C) Error carrection code & its features? (15)

(2)

5495-A

## **SECTION - B**

III. Simplify the following expression & realise using Basic gates.

(A)

$$XY + \overline{XZ} + X\overline{Y}Z(XY + Z)$$

(B)

$$\overline{AB} + \overline{A} + \overline{AB}$$

(C)

$$\overline{AB} + \overline{AB}$$

(15)

IV. Simplify using K-map & draw NAND ckt for simplified expressions.

(A)

$$Y = \overline{A} \overline{B} \overline{C} \overline{D} + \overline{A} \overline{B} C \overline{D} + A \overline{B} \overline{C} \overline{D} + \overline{A} C D + A \overline{B} C \overline{D}$$

(B) Reduce & find simplified SOP form

$$y = \pi M(0,1,2,3,4,6,10,11,13)$$

(15)

## SECTION - C

V. Design & Explain working of

CMOS NAND gate

(15)

VI. Write the specification & charactristics of digital IC's?

(15)

[P.T.O.]

## SECTION - D

- VII. Design & draw 3 bit Gray code Synchronous counter? (15)

- VIII. (A) Explain working of 555 timer as Astable multivibrator. (9)

- (B) Find duty cycle & frequency of Astable multivibrator using 555 timer if

C=0.001 $\mu$ F, RA=2.2K $\Omega$ , R<sub>B</sub>=90K $\Omega$  (6)

## SECTION - E

- IX. (a) What is a universal shift register? Explain

- (b) A certain memory stores 8K x 16 bit words. How many data input lines, data output lines & address lines does it have? What is its capacity in bytes?

- (c) Prove that  $\overline{ABC}$   $(\overline{A+B+C}) = \overline{A} \overline{B} \overline{C}$ .

- (d) How do open collector output differs from Totem poll output?

- (e) What is Inhibit gate. Realise Inhibit gate using NAND, NOR gates.

- (f) Make comparison between DTL & TTL logic families?

- (g) What are the shortcoming of J-K flipflop & how it can be removed?

- An astable multivibrator uses 555 timer. It is required that duty cycle is  $0.5 \& \text{frequency} = 10 \text{KH}_Z$  & C =  $0.001 \, \text{H}^{\circ}$ . Calculate R<sub>A</sub> & R<sub>B</sub>?

- Write the design procedure steps for the design at synchronous counter?

- (i) Explain the diffrence between Minterm & Maxterm?

Total No. of Questions - 91 (2118)

Total Pages: 3

## 5914

## **B.Tech. IIIrd Semester Examination**

## DIGITAL ELECTRONICS (EE/ECE/CSE/IT/EEE) Paper - EC(ID)-3001

Time: Three Hours

()

[Maximum Marks: 100

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary/ continuation sheet will be issued.

Note: Attempt one question from each Section A, B, C & D and the entire Section E.

#### SECTION-A

Fill in the blanks shown with ?

| Binary    | Octal   | Decimal | Hexadecimal |

|-----------|---------|---------|-------------|

| 1011 1101 | ?       | ?       | 7           |

| ?         | 7654321 | ?       | ?           |

| ?         | ?       | 123456  | ?           |

| ?         | ?       | ?       | 1234        |

- What is Hamming code ? Discuss.

- (b) Perform Binary addition: 1010111 + 1111000.

- (c) Perform Binary Subtraction: 11111111 10101010.

15

5914/1900/GGG/98

[P.T.O.

#### SECTION-B

Simplify following Boolean function using quine Mccluskey procedure :

$F(w, x, y, z) = \Sigma(2, 3, 6, 7, 8, 9, 12, 13 + \Sigma dc (14, 15).$ Verify your result using K Map. 15

- Write down the truth table of Full adder, realize it through

- (i) Nand gates only.

- (ii) Nor gates.

#### SECTION-C

- Explain the operation of a CMOS gate. Draw a half adder circuit using MOS gates. 15

- Draw the diagram of a TTL gate and explain its operation.

## SECTION-D

- Draw a diagram. Write down truth table of various flip-flops. What is a Race around condition? How is it eliminated in Master Salve J-K flip-flop ? Draw its." diagram. 15

- What is a Shift Register ? Explain its operation as SISI, 8. PISO, SIPO, PIPO, Ring counter and Twisted ring counter. 15

5914/1900/GGG/98

2

## SECTION-E

- 9. Write short answers:

- (a) What is a Positive logic and Negative logic ? 6

- (b) Draw the truth table of all logic gates.

- (c) Realize an AND gate using NOR gates only.

- (d) Give comparison between various A-D converters.

- (e) What is Base current Hogging? How is it eliminated?

- (1) What is a Register? List various methods of loading the data into shift register.

- (g). What is the difference between ROM and RAM ? 2

- (h) How Race around condition is eliminated in Masterslave J-K flip-flop?

- (i) Perform following binary subtraction:

0101010 - 11010101

(i) Convert following Binary number into Gray code and vice-versa: - 10101111.

4×10=40

Total No. of Questions - 91 (2119)

Total Pages: 3

## 5124

# B.Tech. If it Semester Examination DIGITAL ELECTRONICS (EE/ECE/CSE/IT/EEE)

Paper: EC(ID)-3001

Time: Three Hours]

[Maximum Marks: 100

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary/continuation sheet will be issued.

Note: Attempt one question each from Sections A, B, C and D, and the entire Section E.

## SECTION-A

- 1. Write short notes on the following:

- (a) Error detection code.

- (b) Error correction code.

- (c) ASCII code.

5×3=15

- 2. (a) Solve  $(100.1001)_2 \times (0.01011)_2$ .

- (b) Convert Binary (1001011)<sub>2</sub> and (111101)<sub>2</sub> to Gray code.

5124/2200/GGG/95

[P.T.O.

- (c) What is the weight of MSB in 16-bit computer and 8-bit computer?

- (d) Solve (57)10 (32)10 using 2's complement method.

- (e) Describe the 9's and 10's complement methods.

3×5=15

#### SECTION-B

- Write the truth table of Full Adder circuit and realise the expression with NOR gate.

- Discuss the procedure to use K-map for simplification of 6 variables in SOP form and simplify the variables using K-map for the function

$f(A, B, C, D, E, F) = \Sigma (0, 1, 2, 3, 16, 17, 18, 19, 32, 33, 34, 35, 48, 49, 50, 51, 60, 61, 62, 63)$

#### SECTION-C

- Explain the comparisons of Digital IC logic family. 15

- What are the advantages of ECL ? Explain how ECL gate works.

#### SECTION-D

Explain the operation of Dual slope A/D converter in detail. Also detail the performance characteristics of A/D converter.  Design a mod-8 synchronous μP counter using T flip-flop.

#### SECTION-E

- 9. Write short answers of the following :

- (a) What are the advantages of Gray code over Binary ?

- (b) Why is a code necessary? Discuss.

- (c) Specify the applications of SSI, LSI, MSI, VLSI and ULSI.

- (d) Draw CMOS, NOR circuit with its working.

- (e) What is the difference between Current sourcing and Current sinking?

- (f) Explain the difference between Combinational and Sequential circuits.

- (g) What are the differences between Decoder/Encoder, Mux/Demux?

- (h) Realise a  $4 \times 1$  multiplexer for the function

$$F = \sum m (0, 3, 4, 7).$$

- (i) Which is the fastest ADC, and why?

- (j) Realise AND, OR, NOT operating performance using NAND gates. 4×10=40

Total No. of Questions - 9] (2116)

5072

B.Tech. 3rd Semester Examination

COMPUTER ORGANIZATION CO

Paper - IT (ID) 3001

Time Allowed: 3 Hours

Maximum Marks: 100

Note:- The candidates shall limit their answers precisely with the answer-book (40 pages) issued to them and no supplementary/continuation sheet will be issued.

Attempt five questions in all selecting at least one question from section A,B,C & D. Section E is compulsory.

#### SECTION - A

- (a) Explain the generations of computers (8)

- (b) Draw the logic diagram of a 2-to-4 line decoder with only NOR gates. Include an enable input. (7)

- What is the difference between serial & parallel transfer?

Using a shift register with parallel load, explain how to convert serial input data to parallel output & parallel input data to serial output.

15

#### SECTION - B

Explain Booth's algorithm for multiplication by taking a suitable example.

5072/1400

4. (a) Explain the difference between hardwired & microprogrammed control. Is it possible to have a hardwired control associated with a control memory?

(6)

(b) Define the following: (i) Micro operation (ii) Micro instruction (iii) Micro program (3x3=9)

#### SECTION - C

- 5. (a) How many times does the control unit refer to memory when it fetches an executes and indirect addressing mode instruction if the instruction is (i) a computational type requiring an operand from memory (ii) a Branch type. (8)

- (b) What must the address field of an indexed addressing mode instruction be to make it the same as a register indirect mode instruction? Explain.

(7)

6. Explain instruction pipelining, its possible conflicts & how you remove them?

## SECTION - D

- 7. (a) What is difference between isolated I/O & memory-mapped I/O? What are the advantage & disadvantage of each?

- (b) Why does DMA have priority over the CPU when both request a memory transfer?

| 3) | 507 |

|----|-----|

|----|-----|

- 8. (a) The access time of a cache memory is 100ns and that of main memory 1000ns. It is estimated that 80% of the memory requests are for read & remaining 20% for write. The hit ratio of read accesses is 0.9. A write through procedure is used.

- (i) What is the average access time of the system considering only memory read cycles?

- (ii) What is the average access time of the system for both read & write requests?

- (iii) What is the hit ratio taking into consideration the write cycles?

- (b) A two way set associative cache memory uses blocks of four words. The cache can accommodate a total of 2048 words from main memory. The main memory size is 128k x 32. What is the size of the cache memory? Explain.

## SECTION - E

- (a) Simplify the boolean function F(A, B, C) = Σ (0, 2, 3, 4, 6) using K-map.

- (b) Draw a space time diagram for a six segment pipe line showing the time it takes to process eight tasks.

- (c) What is the use of control memory?

- (d) What is speed up factor in pipeline computers? 2 [P.T.O]

|            | (4) 5072                                                                                                                                                                                                                         |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (e)        | Define 10P?                                                                                                                                                                                                                      |

| <b>(f)</b> | Define Cache Through in Cache 2                                                                                                                                                                                                  |

| (g)        | What is address space & memory space? 2                                                                                                                                                                                          |

| (h)        | What is page fault? 2                                                                                                                                                                                                            |

| (i)        | Explain the following in 3-4 lines :                                                                                                                                                                                             |

|            | (i) Registers (ii) Multiplexers (iii) high impedence<br>state (iv) use of control unit (v) Assembly language<br>vi) Micro instrucion format vii) stack viii) Two-address<br>instructions (ix) Indirect address Mode (x) software |

[Total No. of Questions :9] (2127)

[Total No. of Printers

5501

B.Tech. 3rd Semester Examination

Computer Organisation (CSE/IT) Construction

Paper - IT (ID) - 3001

Time Allowed: 3Hours

Max. Marks: 100

LIBRARY

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary continuation sheet will be issued.

Note: Attempt one question from each section. Section E is compulsory.

#### SECTION - A

- a) Define Instruction Cycle. Discuss memory reference instruction along with the flowchart. [10]

- b) Draw the functional block diagram of CPU and memory interface. [05]

- a) Draw & Explain the diagram of 3 to 8 line decoder.

[05]

- b) What is the difference between serial & parallel transfer? Using a shift register with parallel load, explain how to convert serial input data to parallel output.

[10]

[P.T.O]

(2)

#### Section - B

- a) Describe the design of hardwired control unit by sequence counter. [10]

- What are the merits and demerits of using a variable length instruction formats [05]

- Explain Booth's algorithm for multiplication with the her of flow chart.

## SECTION- C

- a) Explain the use of stack organization in CPU? How you calculate (a+b) '[c' (d+e)+f] using stack? [10]

- b) What are the basic differences between branch instruction & call subroutine instruction? [05]

- 6. a) Draw a space-time diagram for a five segment pipeline showing the time it takes to process nine tasks? [05]

- b) Discuss addressing modes with suitable example? [10]

## SECTION - D

- 7. a) Why are the read and write control lines in a DMA controller bidirectional? Under what condition and for what purpose are they used as inputs and outputs? [10]

- b) Explain the asynchronous data transfer? [05]

5501/900

|     |      | (3)                                                                                                 | 5501             |

|-----|------|-----------------------------------------------------------------------------------------------------|------------------|

| 8.  | a)   | An address space is specified by 24 bit corresponding memory space b by 16 bit the following: [3+3] |                  |

|     |      | i. How many words are there in the address                                                          | space?           |

|     |      | ii. How many words are there in the memory                                                          | space?           |

|     |      | iii. If a page consists of 2K words, how man & blocks are there in the system                       | y pages          |

|     | b)   | Explain the concept of virtual memory?                                                              | [05]             |

|     |      | Section - E                                                                                         | 4                |

| 9.  | Atte | empt all parts:-                                                                                    |                  |

|     | a)   | What is page fault?                                                                                 | [03]             |

| = 2 | b)   | Explain write back method in cache memo                                                             | ory. <b>[03]</b> |

|     | c)   | What is Microprogram sequencer?                                                                     | [03]             |

|     | d)   | What is the use of control memory?                                                                  | [03]             |

What is the maximum speed up that can be achieved by a pipeline. [03]

|    | (4)                                                | 5501            |

|----|----------------------------------------------------|-----------------|

| f) | What is registers?                                 | [02]            |

| g) | What is use of control unit?                       | [03]            |

| h) | What is high impedance state?                      | [03]            |

| i) | Differentiate between RAM and SAM?                 | [03]            |

| j) | What is page replacement technique.                | [03]            |

| k) | What is an Associative memory?                     | [03]            |

| I) | What is a flipflop. Give the truth table for flop? | SR flip         |

| m) | What is memory hierarchy?                          | [02]            |

| n) | Define register indirect and relative add modes.   | ressing<br>[03] |

Total No. of Questions -

Total Pages: 3

(2118)

B. Tech. Wird Semester Agamination

COMPURE ORDS

(CSE/IT)

Paper: IT(ID)-3001

Time : Three Hours]

5920/1200/GGG/104

[Maximum Marks: 100

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary/ continuation sheet will be issued.

Note: Attempt five questions in all, selecting one each from Sections.A, B, C and D. Section E is compulsory.

#### SECTION-A

- What is Combinational logic circuit? How is it different from Sequential logic circuit ?

- Define Instruction cycle. Discuss memory reference instruction alongwith the flow chart.

- What is a Karnaugh map (K-map) ? Explain its significance. Simplify the Boolean function using K-map.

$F(A, B, C, D) = \Sigma(0, 1, 2, 4, 5, 7, 11, 15).$

[P.T.O.

(b) How many 128 × 8 memory chips are needed to provide a memory capacity of 4096 x 16 ?

#### SECTION-B

- Explain the difference between hardwired control and micro programmed control. Is it possible to have a hardwired control associated with a control memory ?

- Define the following:

- (i) Micro operation.

- (ii) Micro instruction.

- (iii) Micro code.

1+2+2=5

10

Draw a flow chart and explain Booth's multiplication algorithm to multiply two signed numbers. 15

#### SECTION-C

- What are the basic differences between Branch instruction, Call subroutine instruction and Program interrupt?

- (b) Define Interrupt. Give five examples of external interrupts and five examples of internal interrupts. What is the difference between Software interrupt and Subroutine call? 10

- What is Pipelining ? Discuss the arithmetic pipeline.

- 2. (a) What are the different types of Interrupts? Explain the interrupt cycle of computer with the help of a flow chart.

- (b) What is the significance of using state tables and diagrams for sequential circuits? Draw the state diagram of a two-bit binary counter with one control signal to start and stop the counter.

## SECTION-B

- How addition and subtraction is performed with signed-2's complement data? Explain the hardware implementation and algorithm.

- What is Control unit? Explain the working of microprogram sequencer for a control memory in detail.

## SECTION-C

- (a) What are the different addressing modes? Explain the use of each with the help of an example.

- (b) What are RISC and CISC ? Explain their characteristics.

- 6. How instruction level parallelism is achieved using instruction pipeline? What are the different conflicts that can occur and how are they resolved?

2

#### SECTION-D

- Discuss Memory hierarchy in a computer system. Also state memory device characteristics.

- What is Cache memory? Discuss various mapping techniques for transformation of data from main memory to Cache memory.

#### SECTION-E

|   | Atte | empt all parts :                                    |     |

|---|------|-----------------------------------------------------|-----|

|   | (a)  | What is a flip-flop? Give the truth table for JK fl | ip- |

|   |      | flop.                                               | 3   |

|   | (b)  | Name universal gates. Why are they called so ?      | 3   |

|   | (c)  | What is a full adder ? Discuss.                     | 3   |

|   | (d)  | Discuss the characteristics of RISC ?               | 3   |

|   | (e)  | What is DMA ?                                       | 3   |

|   | (f)  | What is Virtual memory ?                            | 2   |

|   | (g)  | Differentiate between RAM and SAM?                  | 3   |

|   | (h)  | What is Page replacement technique.                 | 3   |

|   | (i)  | Differentiate between Multiplexer and Demultiplex   | er. |

|   |      | A 5 MAR. 2                                          | 3   |

|   | (j)  | Draw the ckt. of MOD 6 counters.                    | 3   |

|   | (k)  | What are three address instructions?                | 2   |

|   | (1)  | What is an Associative memory ?                     | 2   |

| í | (m)  | Draw the circuit diagram for Shift register.        | 2   |

|   | (n)  | Define Encoder.                                     | 2   |

|   | (o)  | Define Addressing mode. State their significance    | in  |

|   |      | computers.                                          | 3   |

|   |      |                                                     |     |

Total No. of Questions - 9] (2129)

Total Pages: 4

# 5130

## **B.Tech. IIIrd Semester Examination**

## COMPUTER ORGANISATION (CSE/IT)

Paper: IT(ID)-3001

Time: Three Hours]

[Maximum Marks: 100

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary/continuation sheet will be issued.

Note : Attempt five questions in all, selecting one question each from Sections A, B, C & D. Section E is compulsory.

#### SECTION-A

- (a) How can you divide the evolution of computers over the years into different generations? Give the specifications of different components used in each generation.

- (b) What is the difference between Combinational and Sequential circuits? Explain the Excitation table for J-K flip-flop.

5130/1400/GGG/101

[P.T.O.

- 2. (a) What are the different types of Interrupts? Explain the interrupt cycle of computer with the help of a flow chart.

- (b) What is the significance of using state tables and diagrams for sequential circuits? Draw the state diagram of a two-bit binary counter with one control signal to start and stop the counter.

#### SECTION-B

- How addition and subtraction is performed with signed-2's complement data? Explain the hardware implementation and algorithm.

- What is Control unit? Explain the working of microprogram sequencer for a control memory in detail.

## SECTION-C

- (a) What are the different addressing modes? Explain the use of each with the help of an example. 10

- (b) What are RISC and CISC ? Explain their characteristics.

- 6. How instruction level parallelism is achieved using instruction pipeline? What are the different conflicts that can occur and how are they resolved?

5130/1400/GGG/101

2

## SECTION-D

- (a) What is Priority Interrupt? Design a Priority encoder.

- (b) Explain the process of DMA transfer in computer system.

- 8. (a) Explain the Virtual memory concept. How the logical addresses are mapped with the physical addresses?

- (b) A two way set associative cache memory uses block of four words. The cache can accommodate 1024 words from main memory of size 64 K × 16. Find all the informations required to construct the cache memory.

## SECTION-E

## (Compulsory Question)

- Attempt all the following: .

- (a) What are the different phases of an instruction cycle?

- (b) What are the different types of instruction in computer?

- (c) What is the difference between Microprogram and Microprocessor?

- (d) What is Control memory ?

- (e) Differentiate between Program interrupt and Subroutine call.

- (f) How many clock cycles are required to process 100 tasks in five segment pipeline?

- (g) List the different page replacement techniques when page faults occur.

- (h) Draw K-map for  $F = \sum m(0, 1, 2, 6)$ .

- Differentiate between Write Back and Write Through methods of cache writing.

- (j) List the basic components of Memory management unit.

2×10=20

(Total No. of Printed F

(2127)

#### 5502

## B.Tech. 3rd Semester Examination

## Object Oriented Methods & Programming (CSE/IT)

## Paper - IT (ID) - 3002

Time Allowed: 3Hours

Max. Marks: 100

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary continuation sheet will be issued.

Note: Attempt all Questions.

#### Section - A

Explain in detail various garbage collection strategies. [15]

With the help of an example, explain the concept of inheritance in object-oriented programming. [15]

#### Section - B

Define a class vector. Use overloaded \* (multiply) operator to multiply a vector by a scalar.

#### OR

b) With the help of an suitable example, explain the usefulness of function overloading. [15]

#### Section - C

What is a stream and explain about streams in C++. a) Write a function template for binary search.[10+5]

[P.T.O]

5502

#### OR

Differentiate between multiple and multilevel inheritance. Class B and class C are derived from a base class A and class D is derived from class B and class C. How a member of class D can have direct access on members of class A. [5+10]

#### Section - D

Explain about the basic concepts involved in object - oriented systems design.

#### OR

Explain about the basic concepts involved in object oriented systems analysis. [15]

## Section - E

Differentiate between constructor and destructor.

- Define reference variable. Explain about its application with an example.

- Write a note on top down programing approach.

[5]

Write a note on friend function. d) What are abstract classes?

e)

- [5] [5]

- n' Write a note on Entity relationship modelling.

- What is conversion function? How is it created? [5]

- With the help of an example, explain how objects are passed to functions.

5502/900

Total No. of Questions 9] (2119)

Total Pages: 3

1

# 5133

## B.Tech. IIIrd Semester Examination FUNDAMENTALS OF ECONOMICS (IT)

Paper: HU-3001

Time: Three Hours]

[Maximum Marks: 100

The candidates shall limit their answers precisely within the answer-book (40 pages) issued to them and no supplementary/continuation sheet will be issued.

Note: Attempt *one* question from each section. Section E is compulsory. Section A, B, C & D carry equal marks while Section E carries 40 marks.

#### SECTION-A

- Define Demand. Explain the factors that affect demand.

7, 8

- What is Perfect Competition? How does a firm achieve its equilibrium in the short and long run under this type of market form?

5, 10

5133/900/GGG/104

[P.T.O.

#### SECTION-B

- Define Firm. Explain the objective and types of firm.

- 4. What are the underlying factors which must be taken into account while taking pricing decision?

15

#### SECTION-C

- Analyse the nature of unemployment in advanced and less developed economies.

- What is meant by Trade Cycle? Describe the various phases of trade cycle.

5, 10

#### SECTION-D

- What is meant by the term 'Sustainable Development' ?

Explain the role of capital formation in the economic development of a country.

6, 9

- "British colonialism is also responsible for the economic backwardness of India." Comment upon the statement in the light of India's experience since independence.

#### SECTION-E

## (Compulsory Question)

- 9. Write short notes on the following :

- (a) Exceptions to the Law of demand. (Any two)

- (b) Micro Economics and Macro Economics are complementary to each other.

5133/900/GGG/104

2

- (c) Extension and Contraction in demand.

- (d) Alternative pricing policies.

- (e) Mergers and Takeovers.

- (f) Kinds of Inflation.

- (g) W.T.O.

- (h) Trends in Economic growth.

5×8=40